LLVM Mca : huawei HiSilicon's TSV110 work

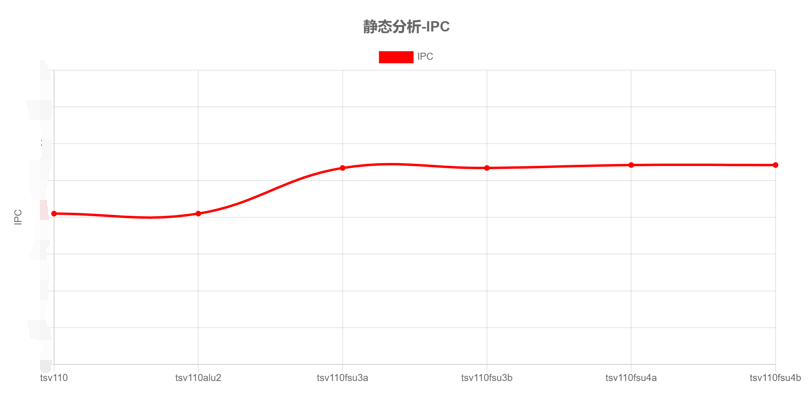

几个对比图

x轴的含义是改变port值的意思,比如tsv110alu2是在tsv110的基础上将alu的值改成2

相关的 git commit

1 | commit c9ca3a3c66a493d72cf7afc7ee975e2de399f2e5 |

只有3个,感觉和2个功能很相关。

最近 Driver commit

复现上面的图

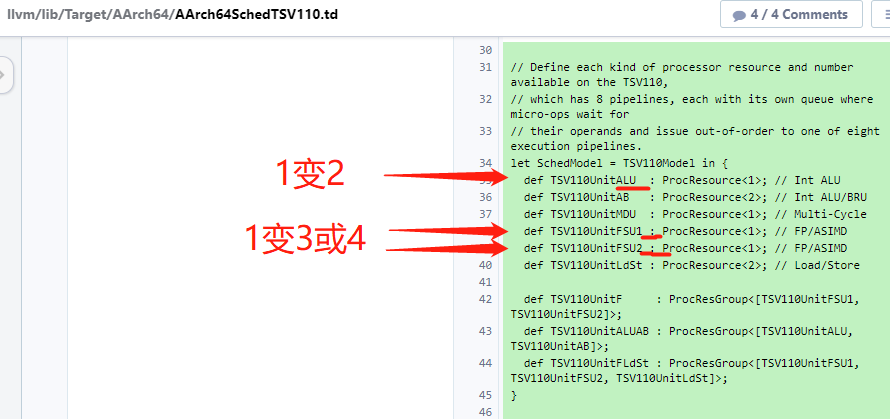

要改的地方

应该每次都要重新编译安装

测试的汇编代码

- 判断

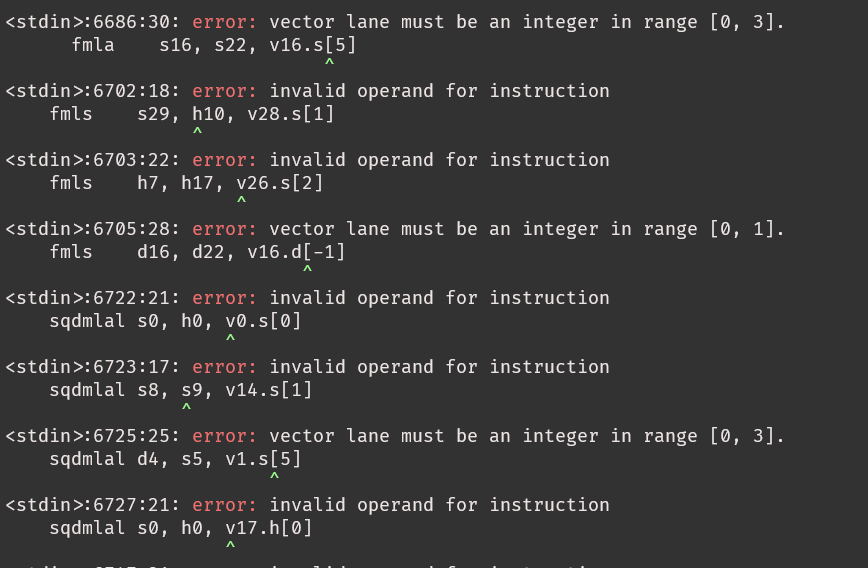

llvm/test/MC/AArch64下的汇编能用吗?选个最大的,neon 不支持, armv8.2也并不支持。感觉有特别要求

1

cat neon-diagnostics.s|llvm-mca -timeline -show-encoding -all-stats -all-views

- 选择osaca的benchmark里的add.c

AArch64SchedTSV110.td

locate at llvm/lib/Target/AArch64/AArch64SchedTSV110.td

td file

tablegen(LLVM class) definitions

部分指令解释

1 | def : InstRW<[TSV110Wr_2cyc_1MDU], (instregex "^(AND|BIC|EON|EOR|ORN|ORR)[WX]rs$")>; |

BIC (bit clear) EON (Exclusive OR) ORR (OR operations on the values in Rn and Operand2)

InstRW的定义

1 | // Map a set of opcodes to a list of SchedReadWrite types. This allows |

TSV110Wr_2cyc_1MDU的定义

1 | def TSV110Wr_2cyc_1MDU : SchedWriteRes<[TSV110UnitMDU]> { let Latency = 2; } |

需要进一步的研究学习

暂无

遇到的问题

暂无

开题缘由、总结、反思、吐槽~~

参考文献

无LLVM Mca : huawei HiSilicon's TSV110 work

http://icarus.shaojiemike.top/2021/10/20/Work/HPC/llvm-mca/LLVM-mca3/