Host-Core With PIM-Core In 3D-stacked Mem

Near Data Processing (NDP) architecture

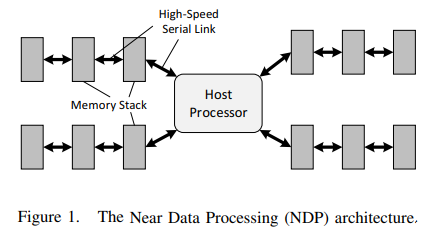

Figure 1 provides an overview of the NDP architecture we study.[^1]

We start with a system based on

- a high-end host processor chip with out-of-order (OoO) cores,connected to multiple memory stacks.

- This is similar to a conventional system where the host processor uses multiple DDR3 memory channels to connect to multiple memory modules,

- but high-speed serial links are used instead of DDR interface.

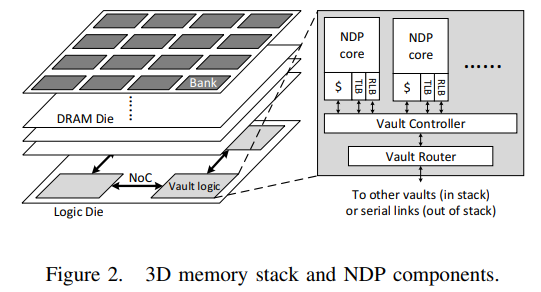

- The memory stacks integrate NDP cores and memory using 3D stacking, as shown in Figure 2.

More Interconnect Design

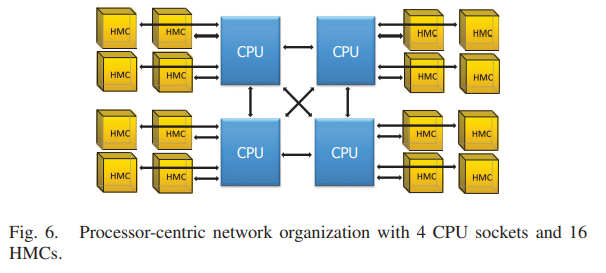

[^2]

[^2]

参考文献

[^1]: PACT’15 Practical near-data processing for in-memory analytics frameworks

[^2]: PACT’13 Memory-centric System Interconnect Design with Hybrid Memory Cubes

[^3]: HPCA’23 best paper DIMM-Link: Enabling Efficient Inter-DIMM Communication for Near-Memory Processing

Host-Core With PIM-Core In 3D-stacked Mem

http://icarus.shaojiemike.top/2023/11/14/Work/Architecture/PIM/HostCoreWithPIMCoreIn3DMem/